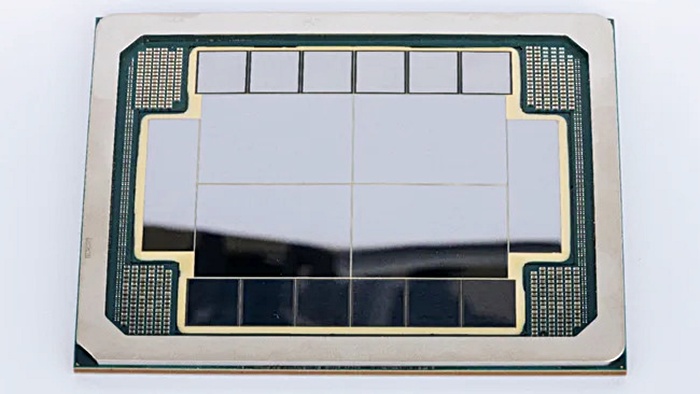

1 月 30 日,英特爾展示了一款名為「AI 晶片測試平台」的先進技術,這款原型系統採用了八倍光罩尺寸的封裝設計,內含 4 個邏輯晶片、12 個 HBM4 級記憶體堆疊及兩個 I/O 晶片。這個展示不僅突顯英特爾在人工智慧(AI)和高效能計算(HPC)應用領域的最新封裝能力,還顯示出其在多晶片設計方面的潛力。

英特爾的這款測試平台並不是一個運行中的AI加速器,而是一個展示未來AI和HPC處理器如何實際組裝的工具。該平台的核心是基於英特爾18A製程技術的四個大型邏輯晶片,這些晶片周圍環繞著HBM4級記憶體堆疊和I/O晶片,並透過EMIB-T 2.5D橋接技術相連。這種設計不僅提高了互連密度,還優化了電力傳輸。

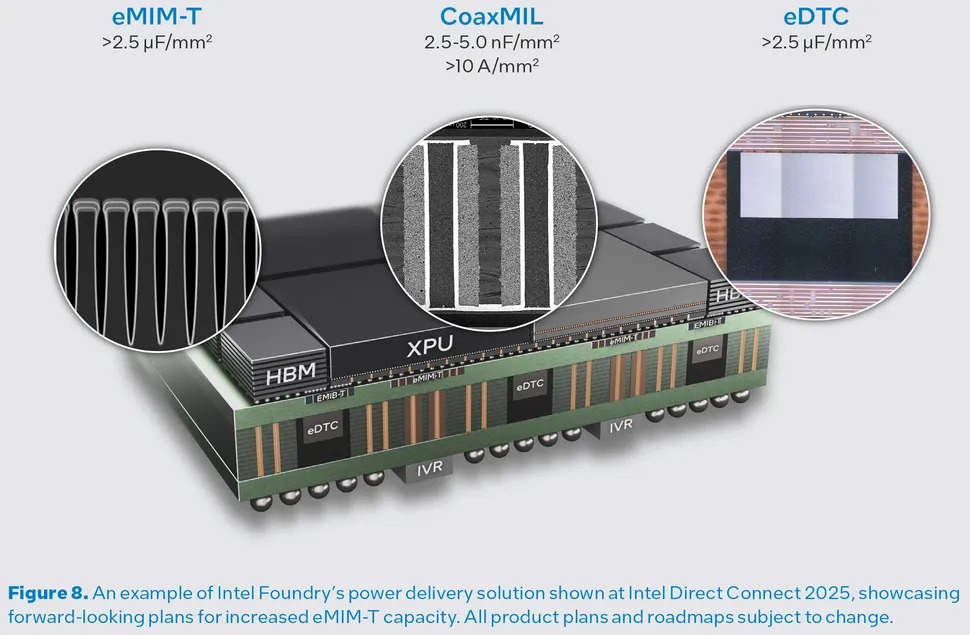

此外,英特爾的測試平台還預示著其向垂直整合的邁進。公司計劃開發專為晶片堆疊設計的18A-PT製程技術,這將使得邏輯晶片或記憶體能在垂直方向上進行堆疊,並且能夠實現更高效的電力供應。

在多晶片AI和HPC加速器的設計中,電力供應是主要的設計約束。英特爾的這個平台結合最新的電力相關創新,旨在支持快速的電流波動,滿足生成式AI工作負載的需求。

儘管英特爾的「AI晶片測試平台」展示了其在技術上的進步,但未來是否會有基於此架構的量產產品仍然有待觀察。英特爾計劃在2027年推出代號為Jaguar Shores的AI加速器,是否會採用目前展示的架構尚不明朗。

(圖片來源:英特爾)